DRAM层次结构

DRAM(Dynamic Random Access Memory),即动态随机存取存储器,最为常见的系统内存。DRAM 只能将数据保持很短的时间。为了保持数据,DRAM使用电容存储,所以必须隔一段时间刷新(refresh)一次,如果存储单元没有被刷新,存储的信息就会丢失。设备关机也会丢失数据,不像磁盘硬盘等存储介质,类似于我们平时笔记本电脑的内存条。

本文对DRAM系统的层次结构,做出了比较清晰直观的解读。

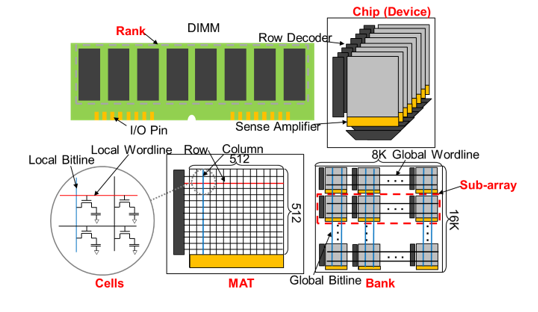

DRAM系统的层次结构

该图为DRAM系统的层次结构图,从顶层到底层包含Rank、Chip、Bank、Sub-array、MAT、Cell。一个Rank由多个Chip并列组成,同步工作,共同驱动内存总线,一个Chip内部包含多个Bank,它们包含独立的行地址译码器和感应放大器,可以并发访问。通常认为,Bank是DRAM完成独立操作的最小单元。但事实上,每个Bank又可以进一步分割为很多的Sub-array(纵向),每个Sub-array包含很多MAT(横向)。每个MAT有独立的局部感应放大器。一个典型的MAT包含512*512个Cell,即存储单元。每个存储单元由一个电容和一个晶体管组成:电容的电荷多少表示数字0或1,晶体管的栅极与字线相连,由字线控制晶体管的导通;晶体管的漏极与位线相连,导通时由位线表示单元里存储的数据。

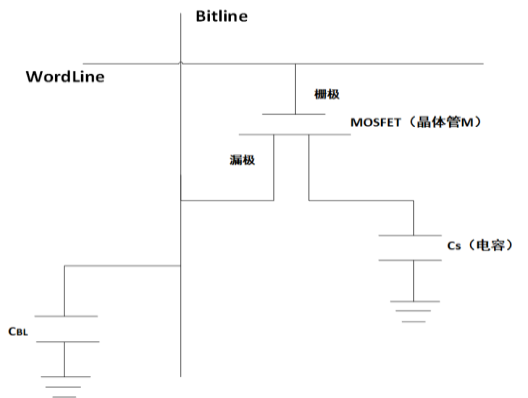

存储单元cell

DRAM的内部结构可以说是PC芯片中最简单的,是由许多重复的“单元”——cell组成,每一个cell由一个电容和一个晶体管(一般是N沟道MOSFET)构成,电容可储存1bit数据量,充放电后电荷的多少(电势高低)分别对应二进制数据0和1。由于电容会有漏电现象,因此过一段时间之后电荷会丢失,导致电势不足而丢失数据,因此必须经常进行充电保持电势,这个充电的动作叫做刷新(Refresh),因此动态存储器具有刷新特性,这个刷新的操作一直要持续到数据改变或者断电。而MOSFET则是控制电容充放电的开关。DRAM由于结构简单,可以做到面积很小,存储容量很大。放大cell的结构,对cell进行分析,了解DRAM是如何通过电容存取数据的。

1、写入数据

如图,向cell中写入数据时,将WL设置为高电平,使晶体管M处于导通状态。此时,Cs和Bitline共享电荷,对Cs进行充电,电压升高到Vs,Bitline处于高电平,写入1;对Cs进行放电,电压降到0,Bitline处于低电平,写入0。

2、读取数据

从cell中读取数据时,同样,首先将WL设为高电平,使晶体管M处于导通状态,逻辑电路通过Bitline感知Cs电荷的重新分配,从而读取数据。具体过程如下:首先,对Bitline进行Precharge,即将Bitline上的电压升到Vs/2,这样的话一旦M处于导通状态,如果cell中保存了1,那么Cs中电压为Vs,与Bitline上电压存在电压差,电荷会从Cs流出到Bitline,使Bitline上的电压升高。cell之外的一个逻辑电路块可以感知这种变化,从而读出数据1。同理,若cell保存的是数据0,那么Cs中电压为0,则Bitline中电荷流出,电压降低,电路感知到这种变化,读出数据0。

注意:由于这种读取操作造成电荷的流入流出,是破坏性的。因此,读操作之后需要Refresh操作,恢复Cs的电荷状态。

原文作者: malizhen

原文链接: http://malizhen.github.io/2019/06/12/DRAM层次结构/

版权声明: 转载请注明出处(必须保留原文作者署名及原文链接)